続、Encore ZIF G4 も ClockUp

2002.04.21 初出

2002.04.28 更新

▼はじめに

毎回云うのもナンですが、改造は自己責任でお願いします。お願いです。この頁の記述に間違いがあっても私は知りません。と云いますか、あったら教えて下さい。お願いです。

▼前回までのお話し

Encore G4/400を抵抗移動で450MHz化の話しはこちら。

▼おわらない

野望(?)が復活(?)しました。Sonnet製 Encore G4/400のPLL_CFGを自前で設定出来るようにしてしまおう!って話しです。

ZIFソケットに出ているPLL_CFGがEncoreの基板に出ていれば、それを流用してMacの母基板側でPLL_CFGを設定出来るんですけどね。残念ながらEncoreには繋がっていないようです。仕方がないので自前でヤってしまいましょう。

▼PLL_CFGを探れ!

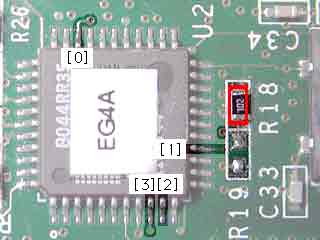

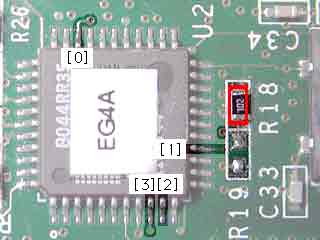

回路を追いかけてみました。先ずは画像を御覧下さい。

基板裏面のispLSI2032VEの辺り

基板裏面のispLSI2032VEの辺り

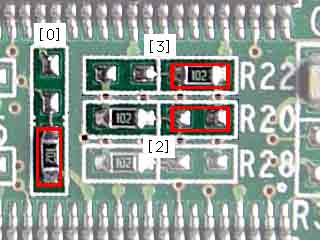

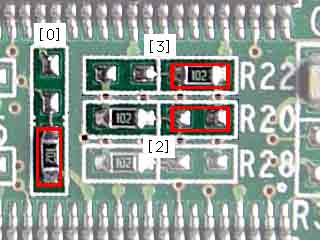

基板表面のRAM辺り

基板表面のRAM辺り

ispLSI2032VE(「EG4A」のシールが貼付してあるチップ)の出力は、プルアップ/ダウン抵抗群を経てPowerPC G4へと向います。画像の抵抗群中の赤枠で示したほうがプルアップ側です。2032VEの出力が無ければ、これらの抵抗群でPLL_CFGを設定出来ますね。

私のEncore G4/400のPLL_CFGは、[0]〜[3}が順にプルアップ,プルアップ,プルダウン,プルアップしてありました。2032VEの出力を無くせば、PLL_CFGの設定は前述のプルアップ/ダウンにより[0-3]=[1101]で『6倍』となります。2032VEにはOE(Output Enable)端子があるので、試しにその端子をGNDに落としてみました。うまくイケばCPUはFSBの6倍で動くハズ。ZIFキャリアを使用してJ700/FSB48MHzの環境で確認しましたが、結果はダメでした。OE端子は無視されているみたいです。うーん、残念。

前置きが長くなりましたが、要するに、2032VEの出力回路の配線をカッター等で切るしかなさそうです。PLL_CFGの[0], [1], [3]は2032VEの脇に出たところをカットすれば良さそうですが、[2]の線は何処で切れば良いのやら.... (^^; 。

2002.04.28追記

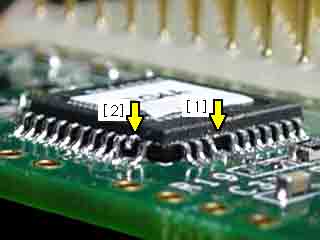

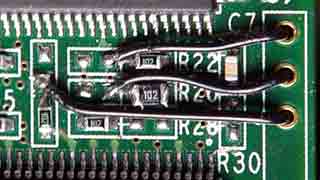

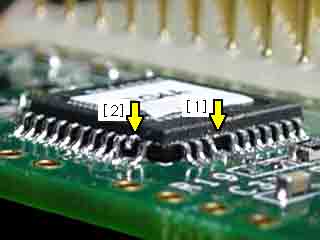

▼配線切断

2032VE脇の配線をカットしても良いのは[0]と[3]でした。[1]と[2]は2032VEチップの下に配線が延びているので、2032VEの端子を浮かせるか若しくは切るしかないでしょう。私は浮かせようと思っていたのですが、[1]のほうが折れちゃいました。後戻りはしない覚悟なので、まぁイイんですけど。って、それを考えると端子を4つともカッターでザクザク切ったほうが簡単確実だったやも。

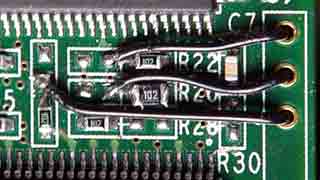

[0], [3]の切断箇所

[0], [3]の切断箇所

[1],[2]の切断箇所

[1],[2]の切断箇所

これで前述の抵抗群によりPLL_CFGの設定が出来るようになりました。

▼お決まり(?)のDIPスイッチ

抵抗群をすべてプルアップ側にして、そしてDIPスイッチでGNDに落とす構成です。回路図は省略して画像のみ紹介。

DIPスイッチと[1]

DIPスイッチと[1]

[0], [2], [3]

[0], [2], [3]

もぅ基板がけっこーボロボロかも (^^; 。

Yosemiteで動作確認をしてみたところ、500MHzで問題無く動きました。GaugeProの結果(7KB/PNG)。550MHzでは起動音のみでした。

▼覚え書き

G3/G4 の PLL_CFG

| PLL_CFG[0-3] |

倍率 |

| 1000 |

x3 |

| 1110 |

x3.5 |

| 1010 |

x4 |

| 0111 |

x4.5 |

| 1011 |

x5 |

| 1001 |

x5.5 |

| 1101 |

x6 |

| 0101 |

x6.5 |

| 0010 |

x7 |

| 0001 |

x7.5 |

| 1100 |

x8 |

| 0000 |

x9(G4のみ) |

| 0110 |

x10(一部のG3のみ) |

▼おわりのおわり

今回改造したEncore G4の基板のRev.は (C)1999 G3G3T-REV-C です。

っとそれから、日本でのEncoreの名称が変更されてCrescendoになってます(Sonnetの製品紹介頁の日本語/英語)。「あんこ〜る」と読んでもらえなかった........とか?

Top > メイン魔神紹介

基板裏面のispLSI2032VEの辺り

基板裏面のispLSI2032VEの辺り 基板表面のRAM辺り

基板表面のRAM辺り [0], [3]の切断箇所

[0], [3]の切断箇所 [1],[2]の切断箇所

[1],[2]の切断箇所 DIPスイッチと[1]

DIPスイッチと[1] [0], [2], [3]

[0], [2], [3]